# Assembly Programming and Computer Architecture for Software Engineers

# Brian R. Hall Champlain College, Burlington, VT

# Kevin J. Slonka

Pennsylvania Highlands Community College, Johnstown, PA

Copyright © 2018 Prospect Press, Inc. All rights reserved.

No part of this publication may be reproduced, stored in a retrieval system or transmitted in any form or by any means, electronic, mechanical, photocopying, recording, scanning or otherwise, except as permitted under Sections 107 or 108 of the 1976 United States Copyright Act, without either the prior written permission of the Publisher, or authorization through payment of the appropriate per-copy fee to the Copyright Clearance Center, Inc. 222 Rosewood Drive, Danvers, MA 01923, website www.copyright.com. Requests to the Publisher for permission should be addressed to the Permissions Department, Prospect Press, 47 Prospect Parkway, Burlington, VT 05401 or emailed to Beth.Golub@ProspectPressVT.com.

Founded in 2014, Prospect Press serves the academic disciplines of Computer and Information Systems by publishing innovative textbooks across the curriculum including introductory, emerging, and upper level courses. Prospect Press offers reasonable prices by selling directly to students. Prospect Press provides tight relationships between authors, publisher, and adopters that many larger publishers are unable to offer in today's publishing environment. Based in Burlington, Vermont, Prospect Press distributes titles worldwide. We welcome new authors to send proposals or inquiries to Beth.Golub@ProspectPressVT.com.

Editor: Beth Lang Golub Production Management: Kathy Bond Borie Cover Design: Annie Clark Cover Illustration: Hanah Leo

eTextbook ISBN: 978-1-943153-31-2

Available from Redshelf.com and VitalSource.com

Printed Paperback ISBN: 978-1-943153-32-9

• Available from Redshelf.com and CreateSpace.com

For more information, visit http://prospectpressvt.com/titles/hall-assembly-programming/

#### About the cover

Why the mountains on the cover? Mountains are both beautiful and forbidding, much like the two foundational topics addressed throughout this book: Assembly Programming and Computer Architecture. They are the source of a challenging journey that opens your eyes to a heightened view of computing. Why the metallic waterfall on the cover? That is just a metaphor for the deep dive into the content that awaits.

# Contents

## Preface

| Chapter 1    |                                            |

|--------------|--------------------------------------------|

|              | Welcome                                    |

|              | Introduction                               |

|              | Computing Languages                        |

|              | Data Representation                        |

|              | Boolean Expressions                        |

|              | 3-bit Computer Example                     |

|              | Summary                                    |

|              | Key Terms                                  |

|              | Code Review                                |

|              | Questions                                  |

|              | Assignments                                |

| Chapter 2    | Processor and System Architecture          |

|              | Introduction                               |

|              | Architecture Overview                      |

|              | Processors                                 |

|              | Input and Output                           |

|              | Summary                                    |

|              | Key Terms                                  |

|              | Questions                                  |

|              | Assignments                                |

| Chapters 1 a | and 2 Supplement More Architecture Details |

|              | Program Loading                            |

|              | Memory Access Improvements                 |

|              | Support Processors                         |

|              | Pipelining and Multi-unit Processing       |

|              | Input/Output System                        |

| Chapter 3    | Assembly and Syntax Fundamentals           |

Introduction

|           | Basic Elements<br>Data Definition<br>Working Examples<br>Summary<br>Key Terms<br>Code Review<br>Questions<br>Assignments                                                           |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Chapter 4 | Basic Instructions<br>Introduction<br>Data Movement and Arithmetic<br>Data Addressing and Transfer<br>Summary<br>Key Terms<br>Code Review<br>Questions<br>Assignments              |

| Chapter 5 | Intermediate Instructions<br>Introduction<br>Boolean Bitwise Operations<br>Branching<br>Repetition<br>Summary<br>Key Terms<br>Code Review<br>Questions<br>Assignments              |

| Chapter 6 | FunctionsIntroductionStack Memory Primerx86 and x86_64 Calling ConventionsImplementationsSummaryKey TermsKey Registers (32-bit, 64-bit)Code ReviewPlatform Specific NotesQuestions |

#### Assignments

Chapter 6 Supplement Program 6.3 x86\_64 Implementation

- Chapter 7 String Instructions and Structures Introduction Accessory Instructions String Primitive Instructions Structures Summary Key Terms Code Review Questions Assignments

- Chapter 8 Floating-Point Operations Introduction Floating-Point Representation Floating-Point Implementations Summary Key Terms Key Registers (32-bit, 64-bit) Code Review Questions Assignments

- Chapter 8 Supplement Chapter 8 Programs Investment Calculator

- Chapter 9 Inline Assembly and Macros Introduction Inline Assembly Macros Summary Key Terms Questions Assignments

- Chapter 10 Advanced Processor and System Architecture Introduction Processor and System Capabilities Interrupts and System Calls

Summary Key Terms Code Review Questions Assignments

Chapter 10 Supplement Chapter 10 Programs and Resources Programs Resources

Chapter 11 Other Architectures Introduction CISC versus RISC More Architectures Quantum Architecture Summary Key Terms Questions

Assignments

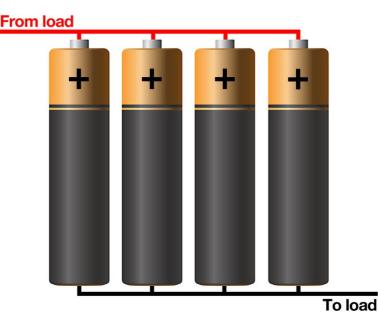

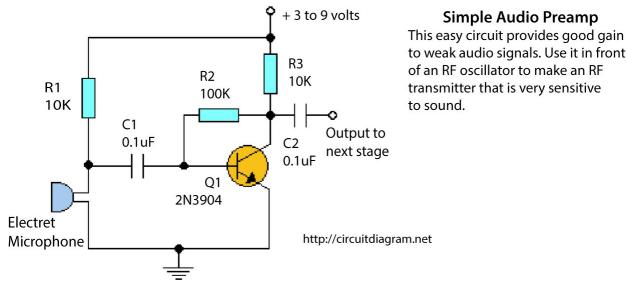

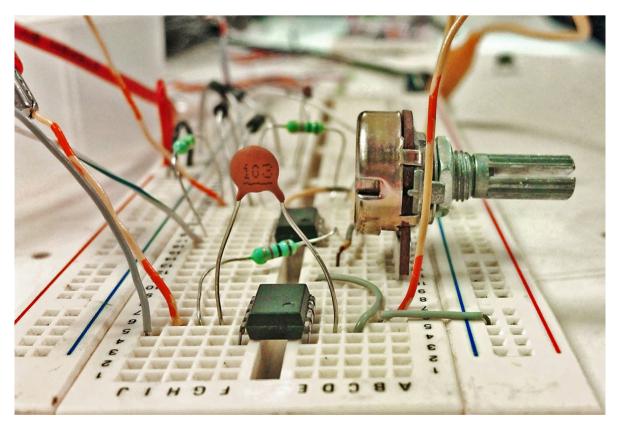

Chapter 12 Hardware and Electrical Components Introduction Foundations of Electricity Electrical Components Integrated Circuits Popular Implementations Summary Key Terms Questions Assignments

Introduction to the Appendices Welcome and Objective Lost and Found

Appendix A Assembly Syntax Translation

Appendix B Environment Setup for Assembly Programming

Appendix C Disassembly

Appendix D Command-Line Debugging Assembly with GDB

Appendix E Linking Assembly and C++

Appendix F Functions and Stack

Appendix G Using CPUID

Appendix H ASCII and Decimal Arithmetic

Appendix I Intrinsics

Index

# Mission of the text

Assembly Programming and Computer Architecture for Software Engineers is an educational examination of Assembly programming and computer architecture. We approach these topics from a practical point of view, addressing *why* and *how* questions throughout the text. We begin by laying the foundation of computer language and computer architecture, and then we delve into Assembly programming as a mechanism for gaining a better understanding of computer architecture, and how Assembly can be used for software development.

Most of the existing books on computer architecture have one or more of the following disadvantages: (1) based on a non-mainstream architecture; (2) written for computer and electrical engineers as opposed to computer scientists and software engineers; (3) focused on a single platform-specific development environment; (4) over-priced; and (5) lacking in practical content. We wanted to give our students something better.

# Audience

Assembly Programming and Computer Architecture for Software Engineers is primarily intended for undergraduate students in computer science and software engineering programs. Prerequisites for this book include introductory computing courses and a solid programming foundation up to and including data structures, preferably in C/C++. Working professionals are also likely to find this book helpful for independent learning and for writing both low-level and high-level code.

# **Book Development and Pedagogical Approach**

The notion to write a book arises every so often in an academic career, with one driver for book ideas being the courses we teach. Both of us teach a course on computer architecture, which has been a staple of computer science and software engineering programs for decades. We also teach in programs where applied and practical skills are foremost.

During our doctoral studies, we made passing comments about writing a book together and at some point we decided that doing so was a real possibility. Writing a book takes a lot of effort, thus our collaboration was essential. So after several years teaching computer architecture and discussing ideas with our wonderful Prospect Press partner, Beth Golub, we arrived at a basic but unique concept. We would write a book for teachers, students, and professionals seeking educational content for computer architecture that overcomes the previously stated disadvantages. Our book is based on mainstream architecture(s), written for computer scientists and software engineers, written for multiple development environments, well priced, and loaded with practical content.

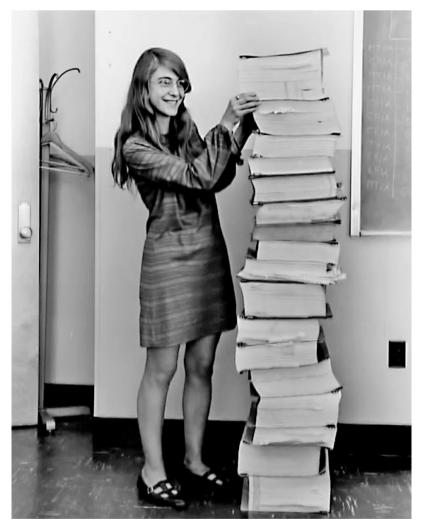

Many hours, days, and weeks have been poured into this text and, in particular, the programs. Writing Assembly code can be infuriating, compelling, and fun, as you are about to discover. Writing about such a complex topic in a clear and efficient manner was also a particular challenge, as was choosing what aspects to cover and when—a classic issue with computing content.

For many computing students, learning about computer architecture via Assembly programming is an advantageous approach. While learning about architecture, useful programming skills are fostered. We knew that a book based on such an approach would help in our courses and was likely to provide a much-needed resource for similar institutions, educators, and students. We did our best and we hope you enjoy learning about Assembly programming and computer architecture the way we enjoy teaching the topics.

# **Organization and Objectives**

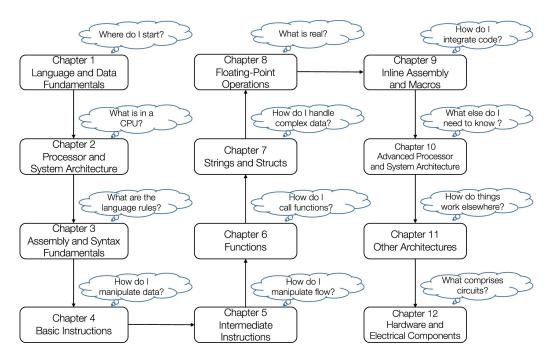

CHAPTERS 1 AND 2 discuss computer language and computer architecture fundamentals.

**CHAPTERS 3** THROUGH 5 introduce x86 and x86\_64 Assembly syntax and a variety of instructions.

CHAPTERS 6 THROUGH 8 cover the more complex topics of functions, structures, and floating-point operations.

**CHAPTERS 9** AND 10 show advanced ways to use Assembly with high-level languages and system software, as well as introduce other advanced aspects of computer and system architecture.

**CHAPTER 11** explores architectures other than x86

**CHAPTER 12** introduces basic hardware principles and components.

# **Chapter Objectives**

- Chapter 1: Describe computer language translation

- Chapter 2: Identify computer and processor components

- Chapter 3: Distinguish between Assembly syntaxes

- Chapter 4: Perform basic arithmetic

- Chapter 5: Control program flow

- Chapter 6: Follow function calling conventions

- Chapter 7: Use strings and structures

- Chapter 8: Execute floating-point operations

- Chapter 9: Integrate low-level and high-level code

- Chapter 10: Issue system calls

- Chapter 11: Compare computer architectures

- Chapter 12: Build simple circuits and devices

# **Supplements**

Chapters 1 and 2, Chapter 6, Chapter 8, and Chapter 10 have additional supplements that provide

programs and content for the respective chapters.

# Appendices

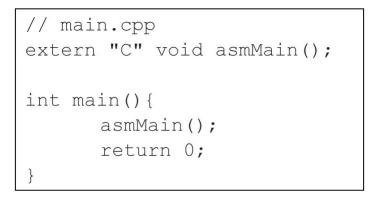

The **INTRODUCTION TO THE APPENDICES** and **APPENDICES A THROUGH I** provide practical information such as resources, translating between Assembly syntaxes, development environment setup, disassembling, debugging, linking Assembly and C++, following calling conventions, using CPUID, performing Decimal and ASCII arithmetic, and using intrinsics.

# Resources

- Book website: http://www.prospectpressvt.com/titles/hall-assembly-programming/

- Book repository: https://github.com/brianrhall/Assembly

- Instructor resources: http://prospectpressvt.com/titles/hall-assembly-programming/instructorresources/

- Student resources: http://prospectpressvt.com/titles/hall-assembly-programming/student-resources/

- Brian's website: http://www.brianrhall.net

- Kevin's website: http://www.kevinslonka.com

- For content-specific resources see the APPENDICES (particularly the INTRODUCTION TO THE APPENDICES) and the WEB RESOURCES links at the beginning of each chapter.

# Acknowledgements

We owe a debt of thanks to the people who have been supportive of our efforts in writing this book. Thank you to the *teachers* who have led us to where we are in our careers. Thank you to *Beth Golub* for giving us the opportunity to publish with Prospect Press and for her wonderful guidance throughout the writing process. Thank you to our *reviewers* for taking time to provide valuable feedback. They include:

John Doyle, Indiana University Southeast Hai Jiang, Arkansas State University Saad Khattak, University of Ontario Institute of Technology Susan Lincke, University of Wisconsin - Parkside Ray Toal, Loyola Marymount University

Thank you to our *colleagues* and *students* for putting up with us clamoring so much about the book over the past two years. And most of all, thank you to our *families* -- for Brian, *Narine* and *Aven*; for Kevin, his fiancé, *Kelli*. Without your tolerance and willingness to sacrifice precious time together, this work would have not been possible. Thank you.

Brian and Kevin

# **CHAPTER 1**

# Language and Data Fundamentals

## **Objectives**

- Distinguish between computing languages

- Identify uses of Assembly programming

- Convert values between number systems

- Solve basic arithmetic problems

- Describe character storage methods

- Evaluate Boolean expressions

- Explain the basics of computer operation

### Outline

- 1. Web Resources

- 2. Welcome

- 3. Introduction

- 4. Computing Languages

- a. Language Relationships

- b. Translation Pipeline

- c. File and Utility Relationships

- d. Why Assembly?

- 5. Data Representation

- a. Number Systems

- b. Integer Storage

- c. Unsigned Integer Storage

- d. Signed Integer Storage

- e. Character Storage

- 6. Boolean Expressions

- 7. 3-bit Computer Example

- 8. Summary

- 9. Key Terms

- 10. Code Review

#### 11. Questions

- a. Short Answer

- b. True/False

- 12. Assignments

# Web Resources

#### Wikis

- https://en.wikibooks.org/wiki/X86\_Assembly (Assembly Programming Overview)

- https://en.wikibooks.org/wiki/X86\_Disassembly (Assembler and Disassembler Overview)

#### Developer

- http://www.unicode.org

- http://www.unicode.org/charts/PDF/U0000.pdf (ASCII)

- http://devimages.apple.com/llvm/videos/LLVM\_Assembler\_Infrastructure.mov (LLVM-MC Overview)

#### Videos

- Video 1.1: Welcome (https://youtu.be/HBwgXY88hyc)

- Video 1.2: Signing Integers (https://youtu.be/vHijiZMbj9E)

- Video 1.3: A 3-bit Computer Example (https://youtu.be/gYczcmDywag)

# Welcome (Video 1.1: https://youtu.be/HBwgXY88hyc)

Welcome to Assembly Programming and Computer Architecture for Software Engineers! The purpose of this book is to provide an educational examination of Assembly programming and computer architecture. Our goal is to approach these topics from a practical point of view. We address questions of *why* and *how* throughout the text. The first two chapters lay the foundation of computer language and computer architecture. The rest of the book uses Assembly programming to help you gain a better understanding of computer architecture, and guides you in using Assembly for software development. What makes this book unique is our multifaceted approach.

- This book is based on a dominant architecture in the computing market—x86 and x86\_64—and what you learn will be transferable to other architectures.

- The programming examples are unique in that we provide code for three common assemblers: GAS, MASM, and NASM. This allows for learning on any OS platform: Mac, Windows, and Linux. This approach also ensures code examples in both AT&T and Intel syntax.

- We provide context and examples in both 32 and 64-bit, both of which are useful for a programmer.

- The Appendices provide practical information to help you learn and use the technologies associated with Assembly and architecture.

- Chapter Supplements provide a deeper dive into topics as necessary.

- We provide links to wikis, developer resources, and videos to assist in further exploration of topics.

- We use Attention notes, Programming notes, and Learning notes throughout the text to guide the reader in beneficial ways.

PROGRAMMING

LEARNING

ATTENTION: The GNU Assembler (GAS) is primarily a Linux-based assembler used by the GNU project and has been developed since 1987. GAS is part of the GNU Binutils package and is used to assemble the Linux kernel amongst other software. The Netwide Assembler (NASM) is a Linux-based open-source assembler/disassembler for x86 and x86\_64 that has been developed since 1996 by very small team of developers. The Microsoft Macro Assembler (MASM) is a proprietary assembler for Microsoft's operating systems, which is packaged with Visual Studio. MASM has been developed since 1981.

• For the sake of our students, we have focused on keeping this text educational, useful, and affordable.

We hope you enjoy this book and find it beneficial in your education and career. Happy learning and coding!

Brian

Figure 1.1 Chapter roadmap

# Introduction

The purpose of this chapter is to introduce fundamental concepts of computer programs and computer architecture. We cover relationships between computing languages and Assembly language's place in the language hierarchy. We discuss the basics of data representation, number systems, and Boolean expressions. Additionally, we illustrate chapter concepts with a 3-bit computer system. This chapter will prepare you for a deeper dive into a specific architecture, x86/x86\_64 in CHAPTER 2, and for understanding Assembly fundamentals beginning in CHAPTER 3.

# **Computing Languages**

### Language Relationships

As programmers, we live in a world of computer languages. Understanding where Assembly fits in the computer language hierarchy is important. Typically, we write code in a high-level language, which simply means that the statements are roughly English-like. Throughout this text we use the high-level language C++ in examples. An example of the English-likeness of a high-level language would be the if...else control structure.

| Example 1.1 ifelse control struct |

|-----------------------------------|

|-----------------------------------|

| English-likeness               | C++                                               |

|--------------------------------|---------------------------------------------------|

| if (this is true) {            | if ( x == y ) {                                   |

| perform this series of actions | cout << "X and Y are the same";                   |

| }                              | }                                                 |

| else {                         | else {                                            |

| perform this series of actions | <pre>cout &lt;&lt; "X and Y are different";</pre> |

| }                              | }                                                 |

High-level languages and the abstraction they provide are great for humans, but the statements must be translated from high-level to machine-level for execution by a computer. Modern computer processors are made up of billions of transistors that switch between allowing (1) or not allowing (0) the flow of electrical current. A system based on two states is called a binary system. Processors must be fed instructions in numeric binary form; so how do we get from high-level to Assembly to machine-level?

# Translation Pipeline

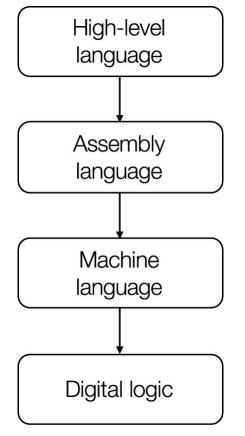

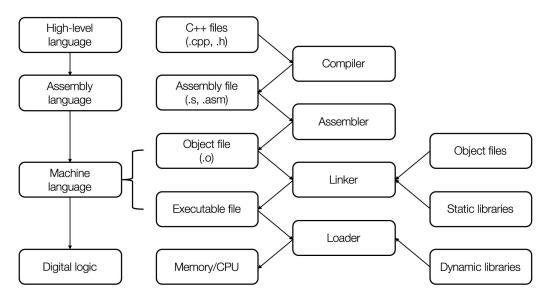

At this point, we want to illustrate the process of moving from high to low level. Using a practical approach, we accomplish this by thinking of the process as a translation pipeline (Figure 1.2).

Figure 1.2 Translation pipeline

# $\langle ! \rangle$

ATTENTION: The "virtual machine" concept is a more abstract way of thinking about levels in machine organization and is used in classical examples. You may encounter the term in other texts and explanations of multilevel design. Virtual machines can be implemented in hardware or software.

A program written in a high-level language must be translated in order to run at a lower level. Translation has two forms: (1) interpreting, which is translating line-by-line as the program executes, and (2) compiling, which is translating all the code in a single step before execution. An example of a high-level interpreted language is Python. An example of a high-level compiled language is C++.

A high-level language statement such as int x = y + 2; has a one-to-many relationship with machine language; that is, each high-level statement corresponds to multiple Assembly and machine instructions.

Assembly is an intermediate form in the translation pipeline. A high-level program is translated into Assembly and the Assembly is further translated into machine language based on a processor's instruction set architecture. The process of Assembly code being translated into machine language is often called encoding. The inverse process of machine language being translated into Assembly is often called decoding.

Assembly language statements have a one-to-one relationship with machine language; that is, each Assembly language instruction corresponds to a single machine language instruction. Machine

language instructions are typically represented in an intermediate numeric form such as hexadecimal, which is then translated and implemented physically as binary on the hardware, what we call digital logic.

# >\_

PROGRAMMING: Some compilers, such as Microsoft's C compiler, translate high-level code directly to machine language, and creating Assembly is an option. Other compilers, such as GCC, translate to Assembly first, then the Assembly code is translated to machine code.

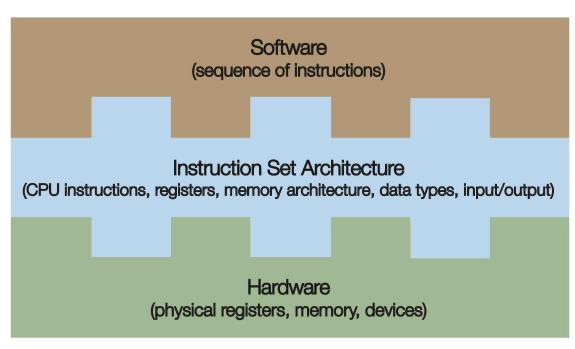

Figure 1.3 Instruction set architecture

An instruction set architecture (ISA) is the programming-related aspect of computer architecture. The ISA specifies the instructions, registers, memory architecture, data types, and other attributes native to a particular processor that are available to a programmer. Think of an ISA as the language a computer speaks. As shown in Figure 1.3, an ISA facilitates communication between software and hardware.

We can think of instruction set architectures as complex or reduced. Complex instruction set computing (CISC) architectures have instructions that are of varying length (in bytes) and are complex in the sense that a single instruction may perform more than one task (e.g., access a memory location and perform arithmetic). An alternative ISA design is reduced instruction set computing (RISC) in which all instructions are the same length and perform only one task (e.g., access a memory location).

x86 and x86\_64 are CISC architectures, while the majority of other ISAs are RISC architectures. CISC attributes of x86 will be shown when instructions are discussed in more detail in CHAPTERS 4 AND 5. Also, when disassembly examples are provided, such as in CHAPTERS 6 and 11, the varying length and complexity of instructions will be evident. You can also see variable length instructions in the CHAPTER 1 PAGE 7 PROGRAMMING note on relocatable machine language.

>\_

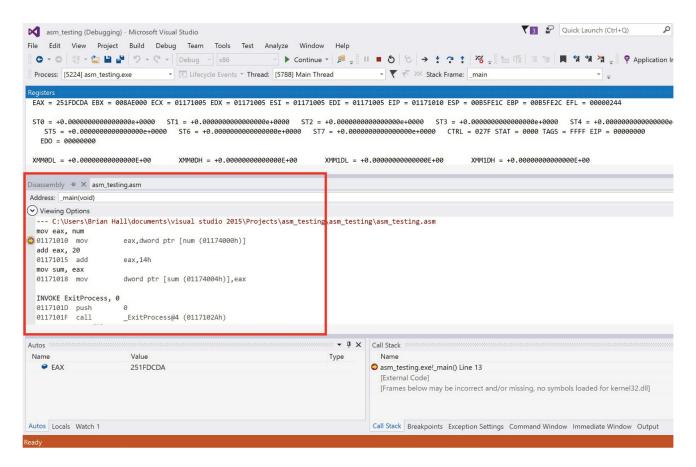

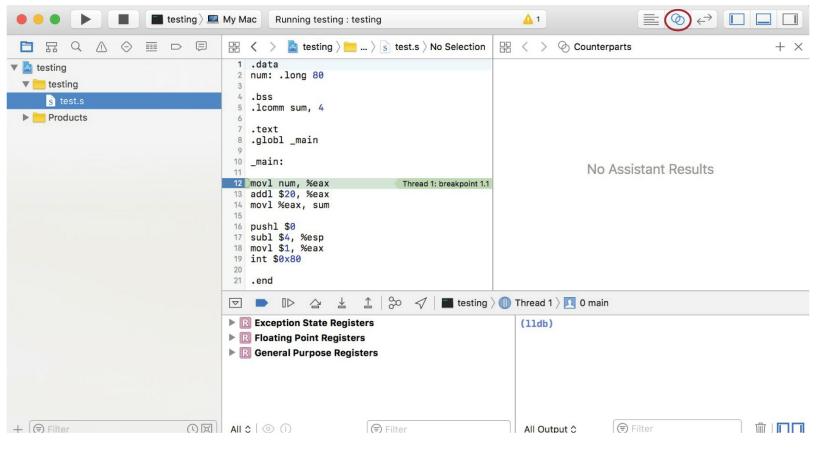

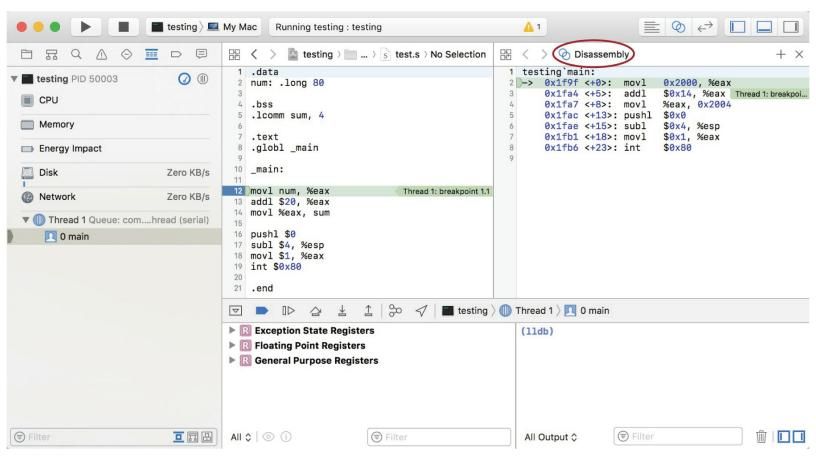

PROGRAMMING: Disassembly is the Assembly code output produced by a disassembler after decoding an object file containing machine language (i.e., decoding machine language bit sequences into Assembly instructions). Most assemblers, compilers, debuggers, and development environments, such as NASM (ndisasm), GDB, LLVM, Xcode, and Visual Studio provide disassembly options. Independent disassemblers are also available such as Capstone, IDA, objdump, and otool. To learn how to disassemble object files, see APPENDIX C: DISASSEMBLY.

Common 32-bit x86 ISA names x86 IA-32 i386 Common 64-bit x86 ISA names x64 x86\_64 Intel: IA-32e (past), Intel 64 (current) AMD: AMD64

ATTENTION: The 32-bit version of the x86 instruction set is commonly known as IA-32 (Intel Architecture 32-bit). IA-32 is synonymous with i386. The 64-bit version of the x86 instruction set is commonly known as x64 or x86\_64, but other names are used depending on manufacturer. The 64-bit version of x86 should not be confused with the 64-bit Intel Architecture (IA-64) used in the Itanium line of processors as it is a completely different instruction set architecture. IA-32 and x64 are not compatible with IA-64.

Table 1.1 provides an example of the translation process. The high-level C++ statement sum = 5; assumes that an integer called sum exists. In Table 1.1, the statement is translated into Assembly using the GNU Assembler (GAS), which uses AT&T syntax. The statement is further encoded into machine language based on the instruction set architecture for an Intel 32-bit (IA-32) processor. The machine language instruction is in hexadecimal form, which is digitally (physically) implemented in binary.

| Level                  | Language                         | Code                                                                |

|------------------------|----------------------------------|---------------------------------------------------------------------|

| High-level<br>language | C++                              | sum = 5;                                                            |

| Assembly language      | GNU Assembler, AT&T<br>syntax    | movl \$0x5, -0x8(%ebp)                                              |

| Machine<br>language    | IA-32                            | C745F80500000                                                       |

| Digital logic          | Binary (physical implementation) | 1100 0111 0100 0101 1111 1000 0000 0101 0000 0000<br>0000 0000 0000 |

**Table 1.1** The translation process

Next, we reinforce the translation process by presenting three encoded Assembly instructions in Example 1.2. Here, the specifics are not the focus, but rather the concept. **CHAPTERS 4** and **5** discuss instructions in further detail.

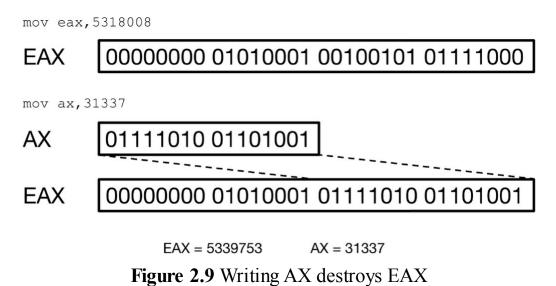

Assume we have the 32-bit Assembly instruction: MOV = ax, 5 If abstracted to a higher-level statement, this is similar to saying something like variable = 5; but more specifically we are saying to move (copy) the immediate value 5 to the *eax* register in Intel Assembly syntax. The MOV instruction is an opcode and *eax* is a register, both of which are specified as part of the IA-32 instruction set architecture. The operation of moving an immediate value to the *eax* register has a specific machine language counterpart, which encoded in hexadecimal is B8. The immediate value operand becomes part of the instruction.

| Example 1.2 Assembly | instructions end | coded into Intel | 32-bit machine l | anguage       |

|----------------------|------------------|------------------|------------------|---------------|

| 1 2                  |                  |                  |                  | $\mathcal{O}$ |

|          | Assembly language       | Machine language |

|----------|-------------------------|------------------|

| MOV eax, | 5                       | B8 05 00 00 00   |

| MOV eax, | 32555                   | B8 2B 7F 00 00   |

| MOV ebx, | 5 ;a different register | BB 05 00 00 00   |

Machine language is numeric, so it is helpful to understand number systems, specifically hexadecimal and binary. Machine language is also specific to a processor. Processor families understand a common machine language, so code written for x86 or x86\_64 processors will run on any processor that is part of that family.

# >\_

PROGRAMMING: Assembly code is not portable across processor families. For example, code written for the x86 processor family will not run on processors such as SUN Sparc, IBM 370, and ARM Cortex.

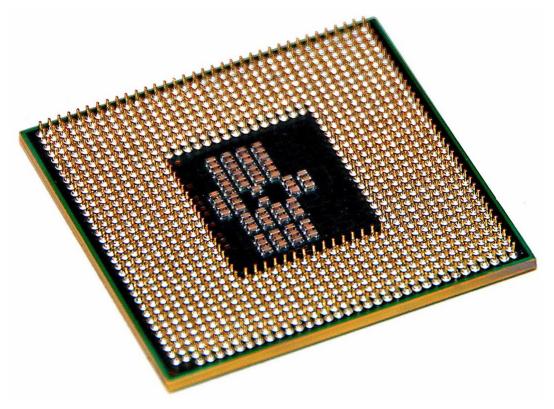

The x86/x86\_64 processor family includes Intel processors such as Pentium, Core-Duo, and Core i7, and AMD processors such as Athlon, Phenom, and Opteron. Both Intel and AMD implement the x86 instruction set as part of their processor design, but the processor design techniques used to implement the instruction set, also known as the microarchitecture, are very different.

Figure 1.4 File and utility relationships

#### File and Utility Relationships

Considering file and utility relationships in relation to the translation pipeline is also helpful. Figure 1.4 illustrates the language levels in relation to files, and also the role of computer utilities that translate one language into another.

The role of a compiler is to translate high-level source code into the intermediate form of Assembly based on the processor's instruction set. The role of the assembler is to encode Assembly code into object code, which is relocatable machine language formatted for a specific operating system (OS) platform. Table 1.2 lists common object file formats by OS platform. The role of the linker is to combine multiple object files and static libraries into a single executable file. The role of the loader is to take the executable instructions contained in the executable file produced by the linker, along with dynamic libraries, and load the machine code into memory for execution by the central processing unit (CPU).

PROGRAMMING: What do we mean by "relocatable" machine language? When Assembly code is assembled into object code, the code is in a generic form with the first instruction starting at address 0x0h and subsequent instruction addresses are offsets based on the preceding instructions' sizes in bytes. When the program is actually loaded into memory, the first instruction will have a legitimate address, with the subsequent instruction addresses based on the offsets.

| Relocatable machine language |                                |      | Running machine language |  |        | e              |              |                          |  |

|------------------------------|--------------------------------|------|--------------------------|--|--------|----------------|--------------|--------------------------|--|

| 00000005                     | b80a000000<br>48<br>bb05000000 | decl | %eax                     |  | 0x1fb2 | <+5>:<br><+6>: | decl<br>movl | \$0xa,<br>%eax<br>\$0x5, |  |

| d000000b                     | с3                             | retl |                          |  | 0x1fb7 | <+11>:         | retl         |                          |  |

#### Table 1.2 Common object file formats by OS platform

| Windows                | macOS  | Linux                   |

|------------------------|--------|-------------------------|

| COFF, PE, Win32, Win64 | Mach-o | ELF, a.out (deprecated) |

# Why Assembly?

An important and reasonable question that we must ask and answer is "Why learn Assembly?" What is the benefit of knowing low-level details if we can write code in high-level languages? The answer to these questions is multifaceted.

- Learning Assembly will enhance your understanding of computer operation. Assembly is a mechanism by which a programmer can learn details of computer hardware, CPU components, memory organization, and the interactions among these elements of computer architecture.

- Programmers make extensive use of a debugger, a utility for troubleshooting code, when writing programs. Debuggers provide Assembly, disassembly, register, and memory information so that the programmer can step through programs at a low level. Understanding Assembly language and computer architecture will help with identifying and fixing code bugs.

- Knowledge of Assembly and computer operation helps a programmer make informed decisions about implementation at high and low levels. A programmer can take advantage of the hardware and optimize for efficiency.

- Knowledge of Assembly removes layers of abstraction from tasks such as bit manipulation and function (procedure) calls.

- Some areas of software development rely on intimate knowledge of Assembly, such as programming for embedded devices, programming device drivers, and system (OS) programming.

Learning Assembly will give you a fuller understanding of how computers operate and how code

executes, which you can use to your advantage. Additionally, from the vantage point of an engineer there is nothing quite as satisfying as talking directly to the processor.

LEARNING: Refer to the **BUBBLE SORT EXAMPLE** at the end of the chapter to consider differences in file sizes and memory footprint for comparable programs written in Assembly and C++.

# **Data Representation**

# Number Systems

Most computers operate physically in binary form. For example, a memory cell is either charged or not charged, a location on disk is magnetized or not magnetized, a transistor in a CPU is either allowing current flow or not allowing current flow. Therefore, binary (1s and 0s) is used to represent data at the lowest level. However, binary is typically difficult for humans to interpret quickly, so other number systems serve as shorthand representations of binary.

LEARNING: Fundamentally, binary is the only number system a computer understands with regard to execution of machine language. So why is binary the number system of computing? *Answer*: The reliability of binary representation and bi-stable environments.

Physical characteristics of binary hardware components:

- The component has two stable energy states, representing 0 and 1. Examples: full on/full off, fully charged/fully discharged, positively charged/negatively charged, magnetized/non-magnetized, reflects light/does not reflect light;

- The two states are separated by an energy barrier (they cannot become each other or be confused);

- Possible to sense the state of the component;

- Possible to switch between the states.

Imagine the complexity of storing a value in a computer based on the decimal or hexadecimal system. A component would have to be able to represent 10 or 16 different states. Using two states makes it much easier to represent physical properties, which in a typical computer are electrical.

Reading and writing low-level code requires programmers to be adept at number systems and formats. The most common formats are binary, octal, decimal, and hexadecimal. Each number system has a base, which indicates the number of symbols available for a digit. Table 1.3 shows details of

common number systems. Decimal and hexadecimal are the most common number system formats used in Assembly code.

Table 1.3 Number systems

| Number System | Base | Digits                          |

|---------------|------|---------------------------------|

| Binary        | 2    | 0 1                             |

| Octal         | 8    | 0 1 2 3 4 5 6 7                 |

| Decimal       | 10   | 0 1 2 3 4 5 6 7 8 9             |

| Hexadecimal   | 16   | 0 1 2 3 4 5 6 7 8 9 A B C D E F |

### Integer Storage

To programmers, the binary number system means 0/1 or false/true. A binary digit is a bit. Bits are combined into bytes to store data like integer (whole number) values. Table 1.4 presents the bits, bytes, terms, and ranges associated with unsigned and signed integer storage. Unsigned means only positive integers are represented, while signed means positive and negative integers are represented.

| Bits     | Bytes    | Term            | Unsigned range          | Signed range                |

|----------|----------|-----------------|-------------------------|-----------------------------|

| 8 bits   | 1 byte   | byte            | $0 \text{ to } 2^8 - 1$ | $-2^7$ to $2^7 - 1$         |

| 16 bits  | 2 bytes  | word            | 0 to $2^{16} - 1$       | $-2^{15}$ to $2^{15} - 1$   |

| 32 bits  | 4 bytes  | doubleword      | 0 to $2^{32} - 1$       | $-2^{31}$ to $2^{31} - 1$   |

| 64 bits  | 8 bytes  | quadword        | 0 to $2^{64} - 1$       | $-2^{63}$ to $2^{63} - 1$   |

| 80 bits  | 10 bytes | tenbyte         | 0 to $2^{80} - 1$       | $-2^{79}$ to $2^{79} - 1$   |

| 128 bits | 16 bytes | double quadword | 0 to $2^{128} - 1$      | $-2^{127}$ to $2^{127} - 1$ |

Table 1.4 Integer storage sizes

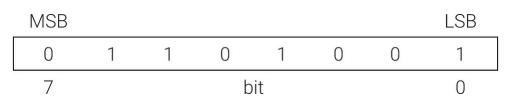

When multiple bits are combined, the leftmost bit is the most significant bit (MSB) and the rightmost bit is the least significant bit (LSB). In the 1-byte example below, if the LSB (bit 0) is changed the value is only altered by 1, but if the MSB (bit 7) is changed the value is altered by 128.

### **Unsigned Integer Storage**

Two useful skills when dealing with number systems is the ability to convert between systems and the ability to perform basic arithmetic like addition. Table 1.5 shows unsigned integer equivalents in decimal, binary, and hexadecimal.

| Decimal | Hex | Binary |

|---------|-----|--------|

| 0       | 0   | 0000   |

| 1       | 1   | 0001   |

| 2       | 2   | 0010   |

| 3       | 3   | 0011   |

| 4       | 4   | 0100   |

| 5       | 5   | 0101   |

| 6       | 6   | 0110   |

| 7       | 7   | 0111   |

| 8       | 8   | 1000   |

| 9       | 9   | 1001   |

| 10      | А   | 1010   |

| 11      | В   | 1011   |

| 12      | С   | 1100   |

| 13      | D   | 1101   |

| 14      | Е   | 1110   |

| 15      | F   | 1111   |

| Table 1.5 Number system | n unsigned | equivalents |

|-------------------------|------------|-------------|

|-------------------------|------------|-------------|

The following nine examples demonstrate ways to perform a variety of unsigned conversions and additions:

- 1. Binary  $\leftrightarrow$  decimal: using a scale of  $2^n$ , where n = bits 1

- 2. Binary  $\rightarrow$  decimal: using positional notation

- 3. Decimal  $\rightarrow$  binary: using division

- 4. Calculating number of bits for a decimal value

- 5. Binary addition

- 6. Hexadecimal  $\leftrightarrow$  binary  $\leftrightarrow$  decimal

- 7. Hexadecimal  $\rightarrow$  decimal: using positional notation

- 8. Decimal  $\rightarrow$  hexadecimal: using division

#### 9. Hexadecimal addition

$\langle \mathbf{I} \rangle$

ATTENTION: Decimal values can be converted to any other base in one of the following ways:

- Scale of *base<sup>n</sup>* (see Examples 1.3 and 1.8)

- Positional notation:  $decimal = (D_{(n-1)} \times B^{(n-1)}) + (D_{(n-2)} \times B^{(n-2)}) + \dots + (D_1 \times B^1) + (D_0 \times B^0)$ where B = base, D = digit, and n = number of digits (see Examples 1.4 and 1.9)

- Division (see Examples 1.5 and 1.10)

In Example 1.3, we show how to convert an 8-bit value between binary and decimal using a Base 2 scale. The conversion is  $00010111_2 = 23_{10}$ . Essentially, you add up the decimal values based on the scale where a 1 exists in the binary sequence.

| Example 1.3 Binary $\leftrightarrow$ decimal (scale $2^n$ ) |     |    |    |     |                |                |                |    |  |  |

|-------------------------------------------------------------|-----|----|----|-----|----------------|----------------|----------------|----|--|--|

| MSB                                                         |     |    |    |     |                |                |                |    |  |  |

| Bits                                                        | 0   | 0  | 0  | 1   | 0              | 1              | 1              | 1  |  |  |

| Base 2 scale                                                | 27  | 26 | 25 | 24  | 2 <sup>3</sup> | 2 <sup>2</sup> | 2 <sup>1</sup> | 2° |  |  |

| Decimal values                                              | 128 | 64 | 32 | 16  | 8              | 4              | 2              | 1  |  |  |

| Add values                                                  |     |    |    | 16+ |                | 4+             | 2+             | 1  |  |  |

| Decimal total                                               |     |    |    |     |                |                |                | 23 |  |  |

In Example 1.4, we show how to convert from binary to decimal using positional notation. The

conversion is  $00010111_2 = 23_{10}$ .

Example 1.4 Binary  $\rightarrow$  decimal (positional notation)

$\begin{aligned} &decimal = (D_{(n-1)} \times 2^{(n-1)}) + (D_{(n-2)} \times 2^{(n-2)}) + \dots + (D_1 \times 2^1) + (D_0 \times 2^0) \\ &decimal = (D_7 \times 2^7) + (D_6 \times 2^6) + (D_5 \times 2^5) + (D_4 \times 2^4) + (D_3 \times 2^3) + (D_2 \times 2^2) + (D_1 \times 2^1) + (D_0 \times 2^0) \\ &decimal = (0 \times 2^7) + (0 \times 2^6) + (0 \times 2^5) + (1 \times 2^4) + (0 \times 2^3) + (1 \times 2^2) + (1 \times 2^1) + (1 \times 2^0) \\ &decimal = (1 \times 2^4) + (1 \times 2^2) + (1 \times 2^1) + (1 \times 2^0) \\ &decimal = (16) + (4) + (2) + (1) \\ &decimal = 23 \end{aligned}$

In Example 1.5, we show how to convert from decimal to binary using division. The conversion is  $42_{10} = 101010_2$ . First, divide the decimal number (42) by the base (2), which results in a quotient of 21 and a remainder of 0. Place the remainder (0) out to the right. The first remainder is the LSB. Then, keep dividing the quotient by the base until nothing is left, placing the remainder to the right after every division. The quotient of the final division (which will be a 0 or 1) is the MSB. The binary sequence is constructed by concatenating the values in reverse order starting with the final quotient as the MSB and the first remainder as the LSB.

| Division      | Quotient | Remaind  | er         |  |  |  |  |  |  |  |

|---------------|----------|----------|------------|--|--|--|--|--|--|--|

| <b>42</b> / 2 | 21       | 0        | LSB        |  |  |  |  |  |  |  |

| 21 / 2        | 10       | 1        |            |  |  |  |  |  |  |  |

| 10 / 2        | 5        | 0        |            |  |  |  |  |  |  |  |

| 5/2           | 2        | 1        |            |  |  |  |  |  |  |  |

| 2/2           | 1        | 0        | $\uparrow$ |  |  |  |  |  |  |  |

|               | →<br>MSB | binary = | 101010     |  |  |  |  |  |  |  |

Example 1.5 Decimal  $\rightarrow$  binary (division)

In Example 1.6, we show how to calculate the number of bits needed to store a given decimal value. For example, the value  $42_{10}$  needs 6 bits of storage.

Example 1.6 Calculating bits for a decimal value

$bits = floor(log_2 n) + 1$   $bits = floor(log_2 42) + 1$  bits = floor(5.392317) + 1bits = 6

LEARNING: When calculating the number of bits needed to store a decimal value, you may be tempted to use  $bits = ceiling(\log_2 n)$ , which would work for most values (like Example 1.6). However, ceiling will result in an incorrect value when *n* is a power of 2, like the value  $32_{10}$ . So,  $ceiling(\log_2 32) = 5$  bits, which is incorrect. We would need 6 bits to store  $32_{10}$ , which is  $100000_2$ .

In Example 1.7, we show binary addition. The rules are simple.

|  | 0 + 0 = 0 | 0 + 1 or $1 + 0 = 1$ | 1 + 1 = 0, carry the 1 | 1 + 1 + 1 = 1, carry the 1 |

|--|-----------|----------------------|------------------------|----------------------------|

|--|-----------|----------------------|------------------------|----------------------------|

#### Example 1.7 Binary addition

| carry |   |   |   |   | 1 | 1 |   |   |                                      |

|-------|---|---|---|---|---|---|---|---|--------------------------------------|

|       | 0 | 0 | 0 | 1 | 0 | 1 | 1 | 1 | 23 <sub>10</sub>                     |

| +     | 0 | 1 | 0 | 0 | 0 | 1 | 1 | 0 | 23 <sub>10</sub><br>70 <sub>10</sub> |

|       | 0 | 1 | 0 | 1 | 1 | 1 | 0 | 1 | 93 <sub>10</sub>                     |

In Example 1.8, we show how to convert between hexadecimal, binary, and decimal. Hexadecimal to binary is based on the rule that each hexadecimal digit is comprised of four bits. The hexadecimal to decimal conversion can be accomplished using a Base 16 scale of  $16^{n}$  (like Example 1.3). The conversion is  $0001101010110111_{2} = 6839_{10} = 1AB7_{16}$ .

Example 1.8 Hex  $\leftrightarrow$  binary  $\leftrightarrow$  decimal

|                     |   | Decimal equivalent of hexadecimal digit |                       | 1 |   |                 | 10 |   |     |                 | 11 |    |                 |         | 7 |     |                  |   |

|---------------------|---|-----------------------------------------|-----------------------|---|---|-----------------|----|---|-----|-----------------|----|----|-----------------|---------|---|-----|------------------|---|

| Convert between hex |   | Hexadecimal                             | Hexadecimal 1         |   |   |                 | А  |   |     | В               |    |    | 7               |         |   |     |                  |   |

| and binary          | l | Bits                                    | 0                     | 0 | 0 | 1               | 1  | 0 | 1   | 0               | 1  | 0  | 1               | 1       | 0 | 1   | 1                | 1 |

|                     | ٢ | Base 16 scale                           | ale 16 <sup>3</sup>   |   |   | 16 <sup>2</sup> |    |   |     | 16 <sup>1</sup> |    |    | 16 <sup>0</sup> |         |   |     |                  |   |

| Convert between hex |   | Decimal values                          | Decimal values 4096 2 |   |   |                 |    |   | 256 |                 |    | 16 |                 | 1       |   |     |                  |   |

| and decimal         |   | Add values                              | (1 x 4096) +          |   | + | (10 x 256) +    |    |   | +   | (11 x 16) +     |    |    | +               | (7 x 1) |   |     |                  |   |

| L                   |   | Decimal total                           |                       |   |   |                 |    |   |     |                 |    |    |                 |         |   | 683 | 39 <sub>10</sub> |   |

In Example 1.9, we show how to convert from hexadecimal to decimal using positional notation. The conversion is  $1AB7_{16} = 6839_{10}$ .

Example 1.9 Hexadecimal decimal (positional notation)

$\begin{aligned} decimal &= (D_{(n-1)} \times 16^{(n-1)}) + (D_{(n-2)} \times 16^{(n-2)}) + \dots + (D_1 \times 16) + (D_0 \times 16^0) \\ decimal &= (D_3 \times 16^3) + (D_2 \times 16^2) + (D_1 \times 16^1) + (D_0 \times 16^0) \\ decimal &= (1 \times 16^3) + (A \times 16^2) + (B \times 16^1) + (7 \times 16^0) \\ decimal &= (1 \times 4096) + (10 \times 256) + (11 \times 16) + (7 \times 1) \\ decimal &= (4096) + (2560) + (176) + (7) \\ decimal &= 6839 \end{aligned}$

In Example 1.10, we show how to convert from decimal to hexadecimal using division. The conversion is  $8039_{10} = 01F67_{16}$ . The process is exactly the same as in Example 1.5, except we divide by 16.

| Division          | Quotient | Remainder     |            |

|-------------------|----------|---------------|------------|

| <b>8,039</b> / 16 | 502      | 7             | LSB        |

| 502 / 16          | 31       | 6             |            |

| 31 / 16           | 1        | 15            | F          |

| 1 / 16            | 0        | 1             | $\uparrow$ |

|                   | →<br>MSB | hexadecimal = | 01F67      |

Example 1.10 Decimal  $\rightarrow$  hexadecimal

In Example 1.11, we show hexadecimal addition using the following formula, which applies to any base.

if  $x_i + y_i \ge base(b)$ , then  $z_i = (z_i MODb)$  and carry 1

The addition is  $4B2_{16} + 6A4_{16} = B56_{16}$ . We have denoted  $x_i$ ,  $y_i$ , and  $z_i$  in the left column.

Example 1.11 Hexadecimal addition

| carry                                                                                                                                                                                                                        |                                | 1                  |    |   |                    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|--------------------|----|---|--------------------|

| $\boldsymbol{x}_{i}$                                                                                                                                                                                                         |                                | 4                  | В  | 2 | 1202 <sub>10</sub> |

| ${\mathcal Y}_i$                                                                                                                                                                                                             | +                              | 6                  | Α  | 4 | 1700 <sub>10</sub> |

| $z_{_i}$                                                                                                                                                                                                                     |                                | В                  | 5  | 6 | 2902 <sub>10</sub> |

| $ \begin{aligned} \boldsymbol{z}_i &= \boldsymbol{z} \\ \boldsymbol{z}_i &= \boldsymbol{z} \\ \boldsymbol{z}_i &= \boldsymbol{z} \\ \boldsymbol{z}_i &= \boldsymbol{z} \\ \boldsymbol{z}_i &= \boldsymbol{z} \end{aligned} $ | (B + .<br>(11 +<br>21 <i>M</i> | A) <i>N</i><br>10) | MO |   |                    |

### Signed Integer Storage

ATTENTION: One of the reasons for signing integers is for the purpose of subtraction. Addition circuits are straightforward and easy to implement from an electrical engineering perspective. Three of the basic arithmetic operations are forms of addition: (1) addition, (2) subtraction (adding a negative value), and (3) multiplication (repetitive addition). Therefore, many CPU circuits are addition circuits.

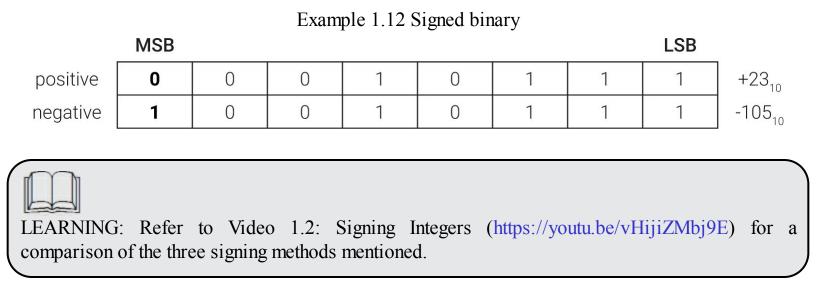

Integers can be signed several ways in a system. Some examples are sign (magnitude) notation, one's complement, and two's complement. In all three methods, the MSB indicates positive (0) or negative (1). Many modern architectures, such as x86 and x86\_64, use two's complement for signing integers. Example 1.12 shows two cases of signed binary values and their decimal equivalents.

Sign notation and one's complement are problematic because both systems have a two zero problem; that is, two forms of zero exist (non-negative and negative), and the methods are more difficult to implement in hardware. Two's complement solves the two zero problem and is based on the additive inverse principle: if you add a number to its additive inverse the sum is zero.

Two's complement is a two-step process: (step 1) flip the bits, and (step 2) add 1. Examples 1.13 and 1.14 are two examples of using two's complement to represent positive and negative integer values in binary.

| Example 1.13 Two's complement of $+23_{10}$ |   |   |   |   |   |   |   |   |   |                                    |

|---------------------------------------------|---|---|---|---|---|---|---|---|---|------------------------------------|

| original value                              |   | 0 | 0 | 0 | 1 | 0 | 1 | 1 | 1 | +23 <sub>10</sub>                  |

| carry                                       |   |   |   |   |   |   |   |   |   |                                    |

| step 1 (flip bits)                          |   | 1 | 1 | 1 | 0 | 1 | 0 | 0 | 0 | 1's complement                     |

| step 2 (add 1)                              | + |   |   |   |   |   |   |   | 1 |                                    |

|                                             |   | 1 | 1 | 1 | 0 | 1 | 0 | 0 | 1 | -23 <sub>10</sub> (2's complement) |

If we were to perform two's complement on the binary value for  $-23_{10}$ , we would arrive back at  $+23_{10}$ .

|                    |   |   | - |   |   |   | - |   |   | 10                                  |

|--------------------|---|---|---|---|---|---|---|---|---|-------------------------------------|

| original value     |   | 1 | 0 | 0 | 1 | 0 | 1 | 1 | 1 | -105 <sub>10</sub>                  |

| carry              |   |   |   |   |   |   |   |   |   |                                     |

| step 1 (flip bits) |   | 0 | 1 | 1 | 0 | 1 | 0 | 0 | 0 | 1's complement                      |

| step 2 (add 1)     | + |   |   |   |   |   |   |   | 1 |                                     |

|                    |   | 0 | 1 | 1 | 0 | 1 | 0 | 0 | 1 | +105 <sub>10</sub> (2's complement) |

#### Example 1.14 Two's complement of $-105_{10}$

# >-

PROGRAMMING: Understanding signed binary is useful, but even more useful is understanding signed hexadecimal, which is what a programmer will typically see in registers and memory when debugging programs.

Signed hexadecimal values using two's complement follows a similar two-step process to that of signing binary values: (step 1) reverse the digits by subtracting each digit from 15 and (step 2) add 1. The quick way to tell if a hexadecimal value is positive or negative is according to the following rule:

If Most Significant Digit (MSD)  $\leq$  7, then value is positive; if MSD  $\geq$  8, then value is negative.

Example 1.15 shows the process of calculating the two's complement of  $+1AB7_{16}$ .

|                         | *            |            |                 |            |                     |

|-------------------------|--------------|------------|-----------------|------------|---------------------|

|                         | $\downarrow$ | if MSD ≤ 7 | 7, then value i | s positive |                     |

|                         | 1            | А          | В               | 7          | +6839 <sub>10</sub> |

| step 1 (reverse digits) | 15 – 1       | 15 – 10    | 15 – 11         | 15 – 7     |                     |

| 1's complement          | 14 (E)       | 5          | 4               | 8          |                     |

| step 2 (add 1)          |              |            | +               | 1          |                     |

| 2's complement          | E            | 5          | 4               | 9          | -6839 <sub>10</sub> |

|                         | 1            | if MSD ≥ 8 | , then value is | s negative | _                   |

Example 1.15 Two's complement of  $+1AB7_{16}$

Here are some other processes for converting signed values between number systems:

- Signed decimal → binary: (1) convert absolute decimal value to binary, and (2) if signed decimal was negative, then calculate two's complement.

- Signed decimal → hexadecimal: (1) convert absolute value to hex, and (2) if signed decimal was negative, then calculate two's complement.

- Signed hexadecimal  $\rightarrow$  decimal: (1) if hexadecimal value is negative calculate two's

complement, (2) convert to decimal, and (3) if original hexadecimal value was negative, then append the negative sign.

When subtracting hexadecimal values, it is much easier to reverse the sign of the value being subtracted by calculating its two's complement and then add the two values.

### **Character Storage**

Characters such as 'A'and '\$' are logical symbols that have to be represented in a numeric way for low-level uses. The guidelines for mapping between characters and their integer representations are defined by character sets, also called character maps or code maps. We will briefly review several of the most common character sets and their relationships to each other.

One of the oldest and most common character sets is the American Standard Code for Information Interchange (ASCII). ASCII is 7-bit (2<sup>7</sup>), which means it can be used to represent 128 unique characters. Much of the ASCII map represents the English alphabet. ASCII is the default character map for high-level languages such as C++. The complete ASCII map can be found on many websites, such as https://en.wikipedia.org/wiki/ASCII.

Table 1.6 ASCII character ranges

| ASCII Range | Characters                       |

|-------------|----------------------------------|

| 0 – 31      | Non-printable control characters |

| 32 – 126    | Printable characters             |

| 127         | Delete (control character)       |

A code map such as ASCII is what facilitates the translation from character to integer. For example, look at the ASCII translation from 'A' and '\$'to their binary equivalents in Example 1.16.

ASCII

Decimal

Hexadecimal

Binary

A

65

41

0100 0001

\$

36

24

0010 0100

Example 1.16 ASCII character translation

ASCII has been extended in several ways to allow for other Latin-based alphabets and symbols. One of the most common standardized character sets developed by the International Organization for Standardization (ISO) and the International Electrotechnical Commission was called ISO/IEC 8859. ISO-8859 extended ASCII by using the eighth bit, which meant 256 (2<sup>8</sup>) characters. Other examples of extending ASCII to eight bits were IBM Code page 437, Windows-1252, and Mac OS Roman. In all of these character maps the standard ASCII range is the same, but they have different encodings for symbols 128-255.

Eventually, around 2008, mapping schemes such as ISO/IEC 10646 and Unicode became more common character sets. These more complex map schemes support more symbols and are backward compatible with standard ASCII. The Unicode character set can be encoded any number of ways. One of the most common encodings is the Unicode Transformation Format (UTF) called UTF-8, which dominates character encoding for the World Wide Web. UTF-8 encodes 1,112,064 characters using one to four octets (a group of 8 bits; a byte). Other Unicode character encodings are UTF-16, which maps characters with one or two 16-bit words, and UTF-32, which maps characters with one 32-bit value.

ATTENTION: A character set such as Unicode defines a list of characters (symbols) with unique numbers, sometimes called "code points" (e.g., A = U+0041). A character encoding, such as UTF-8, is an algorithmic translation for characters to a binary sequence (e.g., U+0041 = 01000001).

The Unicode character set maps a unique logical symbol to a code point comprised of the letter U plus a hexadecimal value as seen in Example 1.17. The UTF encoding then transforms the Unicode character into a binary sequence. The encodings can be expressed using any number system. Notice in Example 1.17 that when using UTF-8, the copyright symbol requires two bytes, which is different than the number sequences in UTF-16 and UTF-32. The example illustrates just how different character encodings (UTFs) can be even when based on the same character set (Unicode).

Example 1.17 Unicode and UTF character translation

| Symbol | Unicode | UTF-8 (binary)    | UTF-8 (hex) | UTF-16 (hex) | UTF-32 (decimal) | C++      |

|--------|---------|-------------------|-------------|--------------|------------------|----------|

| Т      | U+0054  | 01010100          | 0x54        | 0x0054       | 84               | "\u0054" |

| ©      | U+00A9  | 11000010:10101001 | 0xC2 0xA9   | 0x00A9       | 169              | "\u00A9" |

Standard 7-bit ASCII can be thought of as a subset of ISO-8859 and UTF encodings. For example, ASCII encodings are valid UTF-8 when prefixed with a zero in the seventh bit (assuming 0-bit numbering). The first 128 characters of UTF-8 correspond one-to-one with ASCII.

Strings are typically presented as a sequence of characters, which can be based on ASCII or Unicode. For example, the ASCII string "ABC123" is the hexadecimal ASCII sequence 41h, 42h, 43h, 31h, 32h, 33h, 0h. The 0h at the end is the NULL character indicating the end of the string. Keep in mind that when programming and debugging, characters and character sequences will typically be shown as their hexadecimal equivalents. We will discuss strings further in CHAPTERS 3 and 7.

# **Boolean Expressions**

Boolean logic is a foundational topic in computing and programming. Understanding Boolean fundamentals is important for content in later chapters. Boolean expressions allow a programmer to write specific tests for decision structures and provide ways to perform bitwise operations. Boolean

expressions define operations on the values 0/1 or false/true. We cover the four Boolean expressions NOT, AND, OR, and XOR. Different symbols can be used to denote Boolean expressions (Table 1.7), but for our purposes, we will simply use the terms.

Table 1.7 Boolean symbols

| Expression | AND                       | OR                      | NOT                      | XOR                |

|------------|---------------------------|-------------------------|--------------------------|--------------------|

| Math       | ∧ · &                     | V +                     | ¬'~!                     | $\oplus$           |

| C++        | & (bitwise), && (logical) | (bitwise),    (logical) | ~ (bitwise), ! (logical) | $\wedge$ (bitwise) |

| Assembly   | AND                       | OR                      | NOT                      | XOR                |

Boolean expressions operate as follows.

- NOT: reverses (negates) a value

- AND: only *true* if both (all) values are *true*, else *false*

- OR: only *false* if both (all) values are *false*, else *true*

- XOR: *true* if one or the other are *true*, *false* if both are *true* or *false*

#### Table 1.8 NOT Boolean expression

| x | NOT <i>x</i> |

|---|--------------|

| F | Т            |

| Т | F            |

Table 1.9 AND Boolean expression

| x | у | x AND y |

|---|---|---------|

| F | F | F       |

| F | Т | F       |

| Т | F | F       |

| Т | Т | Т       |

Table 1.10 OR Boolean expression

| x | У | x OR y |

|---|---|--------|

| F | F | F      |

| F | Т | Т      |

| Т | F | Т      |

| Т | Т | Т      |

Table 1.11 XOR Boolean expression

| x | у | x XOR y |

|---|---|---------|

| F | F | F       |

| F | Т | Т       |

| Т | F | Т       |

| Т | Т | F       |

In binary, 0 is false and 1 is true. Example 1.18 provides some examples of Boolean operations on binary values.

Example 1.18 Boolean binary expressions

| Given |           |  |

|-------|-----------|--|

| X     | 1110 1101 |  |

| y     | 0110 1010 |  |

Result

| NOT (x)                     | 0001 0010 |

|-----------------------------|-----------|

| AND (x AND y)               | 0110 1000 |

| OR ( <i>x</i> OR <i>y</i> ) | 1110 1111 |

| XOR (x XOR y)               | 1000 0111 |

Each of the Boolean expressions are useful in terms of Assembly programming, as we will see in later chapters. Some examples we cover include using NOT to compute one's complement; AND to align stack and to change letters from uppercase to lowercase; OR to determine if a number is greater than, less than, or equal to zero; and XOR to clear values and determine parity.

Also, AND can be used to turn bits off (0) and OR can be used to turn bits on (1) by using a mask. A mask is a value used to manipulate a bit field in a desired way. Example 1.19 shows three ways to use a mask. The first shows how to turn all bits on in a value by using OR. The second example shows how to turn all bits off using AND. The third is a more practical use of a mask in which we want to query if bit 2 is set (assuming 0-bit numbering); we AND all the bits with 0 except for the

bit(s) we want to test.

| Mask-on using OR           | Mask-query using AND        |                             |

|----------------------------|-----------------------------|-----------------------------|

| 1001 value<br>OR 1111 mask | 1001 value<br>AND 0000 mask | 1101 value<br>AND 0100 mask |

| = 1111 value               | = 0000 value                | = 0100 value bit 2 is set   |

Example 1.19 Masking

## **3-bit Computer Example**

Programmers mostly work in a world of 32-bit and 64-bit systems, but visualizing a system with less bits can be helpful in understanding computing. Therefore, we provide an example of a 3-bit computer system.

| Binary | Sign/Magnitude | One's Complement | Two's Complement | ]                  |

|--------|----------------|------------------|------------------|--------------------|

| 000    | 0              | 0                | 0                | ] _                |

| 001    | +1             | +1               | +1               | leading 0's always |

| 010    | +2             | +2               | +2               | positive           |

| 011    | +3             | +3               | +3               | ]                  |

| 100    | -0             | -3               | -4               |                    |

| 101    | -1             | -2               | -3               | leading 1's always |

| 110    | -2             | -1               | -2               | negative           |

| 111    | -3             | -0               | -1               |                    |

Table 1.12

3-bit computer

Some general rules apply no matter how many bits are in a two's complement system.

- 0 is always all zeros

- -1 is always all ones

- The smallest negative number is always 1 with trailing zeros

- The largest positive number is always 0 with trailing ones

We can examine how computation works in our 3-bit computer with the two's complement representation of integers. The following examples illustrate different scenarios.

|   | Example 1.20 3-bit computation examples |       |  |     |              |   |     |       |   |    |               |   |    |               |

|---|-----------------------------------------|-------|--|-----|--------------|---|-----|-------|---|----|---------------|---|----|---------------|

| - |                                         | #1    |  | ł   | #2           |   | ×.  | #3    |   | ł  | #4            |   | 15 | #5            |

| - | 2                                       | 010   |  | 3   | 011          |   | 2   | 010   | _ | 3  | <b>0</b> 11   | - | -4 | 100           |

|   | + 1                                     | + 001 |  | - 1 | + 111        | _ | - 4 | + 100 |   | +2 | + <b>0</b> 10 |   | -3 | + <b>1</b> 01 |

|   | 3                                       | 011   |  | 2   | <b>1</b> 010 |   | -2  | 110   |   | 5  | <b>1</b> 01   |   | -7 | <b>10</b> 01  |

Evanuela 1 20 2 hit commutation avanuela

In #1, we add two positive numbers and achieve the expected result. In #2, we perform a subtraction by adding a negative. The arithmetic in #2 results in a carry that is dropped because it exceeds the capacity of a 3-bit integer in our 3-bit computer, leaving the expected result. In #3, we subtract again to achieve a negative result within the bounds of the system. In #4, we add two numbers that exist in our 3-bit system but result in a value beyond the bounds of the system. We can detect the overflow scenario by noticing that two positive values result in a negative value (see the leading bits). An overflow scenario causes the overflow bit to be set in the CPU's status register (which will be introduced in CHAPTER 2). In #5, we subtract two negatives that exist in the system but again result in overflow as indicated by two negative values with a positive result. We discuss how overflow conditions are handled beginning in CHAPTER 4.

#### >\_

PROGRAMMING: How does a CPU know an integer is signed or unsigned? Answer: The CPU does not know! The CPU uses Boolean logic to set status flags after arithmetic operations regardless of the scenario. The programmer must decide what flags to interpret or ignore based on the operation. Status flags and related topics are covered further in future chapters, particularly in CHAPTERS 2 and 4.

### Summary

In this chapter we presented the basics of computing via an exploration of computing languages, data representation, Boolean expressions, and a 3-bit computer example. Computing languages form a hierarchy, which we illustrated as a translation pipeline. Assembly language is an intermediate language that allows us to better understand and explore low-level details in computer operations. We also presented methods of data representation for integers and characters using number systems and character sets, respectively. We discussed Boolean expressions, which are a building block for more complex tasks. Lastly, we showed how binary two's complement computation works within a 3-bit computer system. These foundational concepts will prepare you for more advanced topics presented throughout this book.

### **Key Terms**

American Standard Code for Information Interchange (ASCII)

assembler bit byte character encoding character set compiler compiling complex instruction set computing (CISC) computer architecture debugger disassembly high-level language instruction set architecture (ISA) interpreting linker loader machine-level mask microarchitecture object code one's complement reduced instruction set computing (RISC) signed translation pipeline two's complement Unicode unsigned

## **Code Review**

The reason for this Bubble Sort Example and comparison is twofold: (1) to show that Assembly is not as daunting a language as might be initially thought, and (2) to show that well-written Assembly can provide some size and performance gains (keep in mind this is a very simple example).

|          | Memory footprint .s file |      | .cpp file | .o file | executable file |  |

|----------|--------------------------|------|-----------|---------|-----------------|--|

| Assembly | 348kb                    | 346b | N/A       | 1kb     | 9kb             |  |

| C++      | 424kb                    | 21kb | 410b      | 3kb     | 9kb             |  |

| D 111       | 1         | •          |

|-------------|-----------|------------|

| Rubble sort | example – | comparison |

|             | Chample   | comparison |

|             |           |            |

Notice the size difference between the Assembly .s file and the .s file produced by the C++ compiler.

The executable code in the C++ compiler's .s file is about 3kb of the 21kb total, which translates to the sizes seen in the .o file comparison. However, the resulting executable files are comparable, with the Assembly version's memory footprint being slightly smaller.

| # Assembly Bubble Sort     | // C++ Bubble Sort               |

|----------------------------|----------------------------------|

| .data                      | <pre>int main(){</pre>           |

| array: .long 3, 2, 6, 4, 1 |                                  |

| count: .long 5             | int size = 5;                    |

|                            | int value[5] = {3, 2, 6, 4, 1};  |

| .text                      | int i, tmp;                      |

| .globl main                | bool swapped;                    |

| main:                      |                                  |

|                            | do                               |

| mov count, %ecx            | {                                |

| dec %ecx                   | swapped = false;                 |

|                            | for $(i = 0; i < size - 1; i++)$ |

| outerLoop:                 | if (value[i + 1] < value[i])     |

| push %ecx                  |                                  |

| lea array, %esi            | <pre>tmp = value[i];</pre>       |

| ica array, ecor            | value[i] = value[i + 1];         |

| innerLoop:                 | value[i + 1] = tmp;              |

| mov (%esi), %eax           | swapped = true;                  |

|                            |                                  |

| cmp %eax, 4(%esi)          | }                                |

| jg nextStep                |                                  |

| xchg 4(%esi), %eax         | <pre>} while (swapped);</pre>    |

| mov %eax, (%esi)           |                                  |

|                            | return 0;                        |

| nextStep:                  | }                                |

| add \$4, %esi              |                                  |

| loop innerLoop             |                                  |

| pop %ecx                   |                                  |

| loop outerLoop             |                                  |

| push \$0                   |                                  |

| sub \$4, %esp              |                                  |

| mov \$1, %eax              |                                  |

| int \$0x80                 |                                  |

| .end                       |                                  |

Bubble sort example – code

# Questions

### Short Answer

- 1. x86 and IBM 370 are examples of processor \_\_\_\_\_.

- 2. Assembly language statements have a one-to-\_\_\_\_\_ relationship with machine language statements.

- 3. A high-level language statement has a one-to-\_\_\_\_\_ relationship with machine language statements.

- 4. Translating between language layers has two forms: \_\_\_\_\_\_ and \_\_\_\_\_.

- 5. x86 and x86\_64 are examples of \_\_\_\_\_\_ instruction set architecture.

- 6. A "word" is \_\_\_\_\_\_ bits, in terms of x86 architecture.

- 7. \_\_\_\_\_\_ is the fundamental number system of computing due to its reliability.

- 8. \_\_\_\_\_ is the formula for calculating the number of bits needed to store a given decimal value.

- 9. \_\_\_\_\_\_ to \_\_\_\_\_\_ is the numeric range for an unsigned byte.

- 10. When converting from hexadecimal to binary, each hexadecimal digit is represented by \_\_\_\_\_\_ bits.

- 11. On x86 processors, a most significant bit of 1 indicates that the number is \_\_\_\_\_\_.

- 12. In a two's complement system, a hexadecimal value with a leading 7 would indicate the value is

- 13. \_\_\_\_\_\_ to \_\_\_\_\_\_ is the numeric range for a signed byte.

- 14. Character storage is achieved via the use of \_\_\_\_\_\_.

- 15. \_\_\_\_\_\_ is the Boolean expression that results in a false if both inputs are true.

- 16. An \_\_\_\_\_\_ condition is when a computed result goes beyond what can be stored given the computer's architecture.

### True/False

- 1. Assembly is portable across processor families. (T/F)

- 2. Two's complement has the problem of two zeros. (T/F)

- 3. The x86\_64 architecture is not synonymous with IA-64. (T/F)

- 4. An assembler encodes high-level statements into object code. (T/F)

- 5. A CPU inherently understands whether an integer is positive or negative. (T/F)

# Assignments

- 1.1 Explain one practical reason for learning Assembly programming.

- 1.2 Two's complement is based on what mathematical principle and what does the principle mean?

- 1.3 Complete the CHAPTER 1 ACTIVITY SUPPLEMENT.

- 1.4 Challenge Assignment: Disassemble an object file from a high-level language. You may use an object file from an existing C++ project. Use your chosen platform and disassembler. Review APPENDIX C: DISASSEMBLY for help. Examine the output. What are the shortest and longest instructions in bytes?

### **CHAPTER 2**

# Processor and System Architecture

#### **Objectives**

- Recognize components of computer architecture

- Distinguish between memory types and location

- Identify CPU sub-components

- Describe CPU register use in Assembly programming

- Evaluate various Input and Output methods.

#### Outline

- 1. Web Resources

- 2. Introduction

- 3. Architecture Overview

- 4. Processors

- a. Cache and Registers

- b. 64-bit Processors

- c. Instruction Execution

- d. Pipelining

- 5. Input and Output

- 6. Summary

- 7. Key Terms

- 8. Questions

- a. Short Answer

- b. True/False

- 9. Assignments

### Web Resources

#### Wiki

• https://en.wikipedia.org/wiki/X86

• https://en.wikipedia.org/wiki/X86-64

#### Developer

- http://www.intel.com/content/www/us/en/processors/architectures-software-developermanuals.html

- http://developer.amd.com/resources/documentation-articles/developer-guides-manuals/

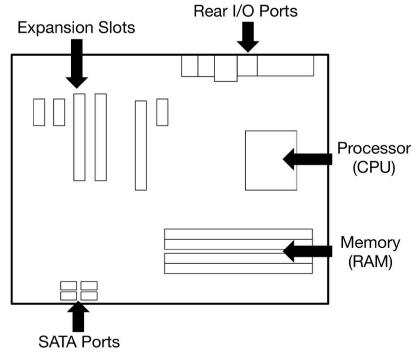

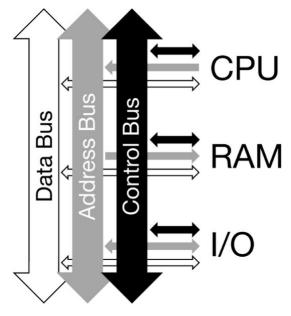

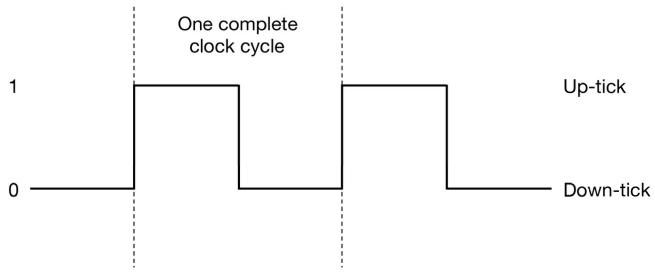

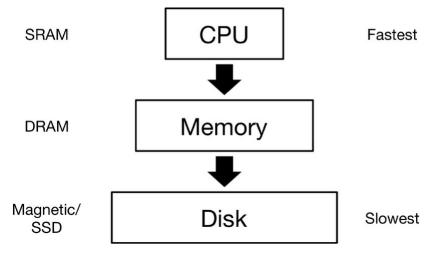

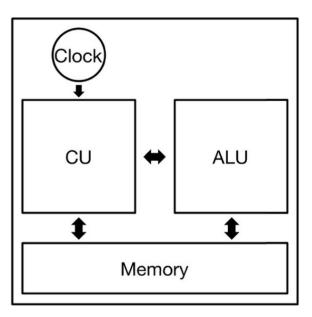

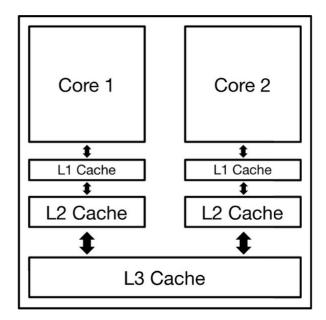

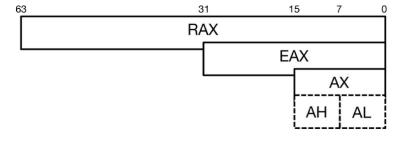

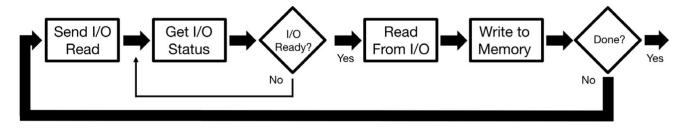

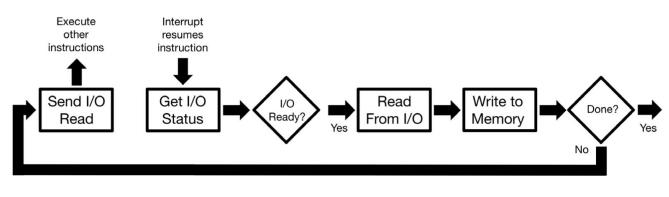

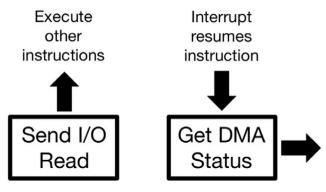

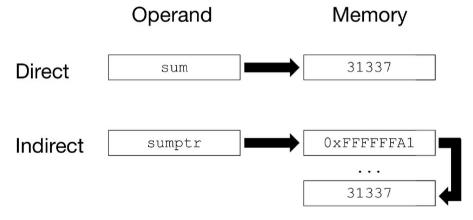

# Introduction